Zprávy

DAC zkoumá roli AI a ML na trzích

Moscone Center, San Francisco, bude hostit DAC 25. - 28. června

Řešení OneSpin a Austemper Design Systems oba zvýrazní nástroje pro ověření funkční bezpečnosti. Austemper se soustředí na kritický vývoj systému s nástrojem KaleidoScope, který podporuje analogovou konstrukci pro souběžné šíření poruch smíšeného signálu. Automatizovaná sada nástrojů nabízí bezpečnostní analýzy, syntézu a ověřovací schopnosti aplikací zaměřených na certifikaci. Používá se pro automatizaci ve velkém měřítku v ADAS a autonomní jízdě. Souběžná simulace poruchy zahrnuje simulace doporučené podle normy ISO 26262 pro splnění požadavků ASIL.

Společnost nedávno spolupracovala s firmou OneSpin Solutions, aby přijala metodologii podporovanou pomocí nástrojů pro aplikace funkční bezpečnosti, která kombinuje konstrukční a ověřovací tok, který bude demonstrován na stánku OneSpin. Mechanismy zabezpečení hardwaru se vkládají do návrhů čipů a nástroje společnosti OneSpin Solutions formálně ověřují logiku zabezpečení hardwaru. Kontrola rovnocennosti zajišťuje, že vložená bezpečnostní logika neovlivní pravidelnou funkčnost a analýza zjišťování závad ověří, zda bezpečnostní mechanismy fungují správně v případě náhodných chyb.

Společnost OneSpin rovněž propaguje svou sadu nástrojů pro odbornou přípravu po ověření procesů vývoje nástrojů společností TÜV SÜD. Počáteční sada je k dispozici pro nástroj 360 EC-FPGA EDA společnosti, což je automatická sekvenční kontrola rovnocennosti, která zabraňuje návrhovým tokům FPGA při zavádění implementačních chyb. Sada je certifikována podle ISO 26262, IEC 61508 a EN 50128.

FPGA pohledy

Stále s FPGA designem, Zkusit spolupracuje s firmou Xilinx a nabízí platformu Vivado v oblaku prostřednictvím platformy Plunify Cloud. Návrháři zaplatí jen 50k, aby sestavili projekt Vivado na cloudovém serveru Amazon Web Services (AWS), včetně licencí.

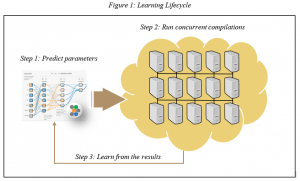

Společnost také prokáže vylepšení svého časového uzávěru InTime pro optimalizaci časování FPGA v cloudu (obr. 1). Metoda optimalizace InTime může zlepšit frekvenci hodin o 20 až 80% a splnit požadavky na časování ve dnech, spíše než v týdnech prostřednictvím strojového učení. Software také urychluje uzavírání a optimalizaci časování a je dostupný přes cloud.

Společnost také prokáže vylepšení svého časového uzávěru InTime pro optimalizaci časování FPGA v cloudu (obr. 1). Metoda optimalizace InTime může zlepšit frekvenci hodin o 20 až 80% a splnit požadavky na časování ve dnech, spíše než v týdnech prostřednictvím strojového učení. Software také urychluje uzavírání a optimalizaci časování a je dostupný přes cloud.

Podpora technologie eFPGA, Achronix Semiconductor spolupracuje s odborníkem na IP OBSAZENÍ zvyšovat propustnost a úsporu paměti.

Dva vystavovatelé vysvětlí, jak byla CAST bezztrátová kompresní IP přenesena do portfolia Achronix FPGA pro použití v aplikacích datových center a mobilních datových přenosů dat. Hardwarová implementace standardu komprese bez komprese pro systémy Deflate, GZIP a ZLIB je kompatibilní se softwarovými implementacemi používanými pro kompresi nebo dekompresi, které zajišťují propustnost až 100Gbit / s s nízkou kompresí a nízkou latencí, spolu s technologií Speedfore eFPGA pro přesun a ukládání velkých data s nízkou spotřebou energie.

CAST přenesl své IP na FPGA společnosti Achronix

Energetická účinnost

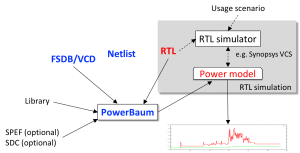

Když už mluvíme o řízení spotřeby, Baum, označuje energetickou účinnost za nejvíce nevyužitou oblast v návrhu čipů. Automatizovaný nástroj pro analýzu a modelování energie je určen pro projekty v oblasti automobilového průmyslu, internetu, mobilních sítí a serverů. PowerBaum 2.0 (Obrázek 3) podporuje dynamické a statické napájení, přičemž používá RTL a netlist popisy a přidává podporu pro analýzu napájení s hardwarovou emulací. To říká společnost, dovoluje inženýrům opravit chyby napájení v realistických softwarových scénářích. Nástroj také podporuje analýzu s libovolnými teplotami, které specifikují konstruktéři, aby vyhodnotili účinky teploty na spotřebu energie návrhu.

U společnosti DAC společnost také představí PowerWurzel, analyzátor motoru na úrovni vrtu, který bude integrován s PowerBaum pro modelování výkonu.

Obrázek 3 Baumovy nástroje analyzují energetickou účinnost

Cloud-based SoC design a verifikační nástroje pro návrh IC od Metriky zahrnout Simulátor oblaků a Správce ověření, určený ke správě simulačních požadavků a zdrojů a přizpůsobení je každou minutu nahoru nebo dolů. Společnost tvrdí, že služba Google Cloud umožňuje neomezenou simulaci systému SystemVerilog v souladu s UVM a přirozený management ověřování na webu pro rychlejší regresní časy, snížené chyby kódového kódu a předvídatelné krytí kódu.

Vedle vystavovatelů se na události konají technické zasedání a program klíčových poznámek věnovaných aktuálním oblastem. V letošním roce bude například Cadence hostit tutoriál na téma "Funkční bezpečnost a spolehlivost pro automobilové aplikace" a jeden na strojovém učení ("Strojové učení přijímá výkon rozpoznávání řeči na další úroveň"). Klíčová poznámka Anny-Katriny Shedletsky, Instrumental, se v pondělí 25. června zaměří na "automatizaci inteligence: strojní učení a budoucnost výroby". Využití technologie ML a AI pro sociální pomocnou robotiku (SAR) zkoumá ve čtvrtek Keyina Matarić, univerzita v jižní Kalifornii, která bude prezentovat "Automatizace a zvětšení: sociální pomocné roboty a budoucnost práce".

Další myšlenka obhajuje RISC-V jako prostředek k uvolnění architektů z architektury architektury proprietárních instrukcí (ISA). David A Patterson, Google a Kalifornská univerzita představí "Nový zlatý věk pro počítačovou architekturu: specifické akcelerátory domény a otevřené RISC-V".

Novinkou tohoto roku v DAC je architektonická infrastruktura. Iniciativa Komise ESD Alliance a sdružení pro vysoce výkonné výpočetní profesionály je oblast věnovaná IT infrastruktuře pro návrh elektronických systémů a komponent. Kromě požadavků na výpočet a ukládání dat pro návrh a správu využití cloudu je k dispozici specializované pavilon Design-on-the-Cloud, které se zabývá problematikou správy licencí, výpočetní sítě a zabezpečení dat.