# MC92604 Dual Gigabit Ethernet Transceiver Reference Manual

MC92604RM Rev. 1, 06/2005

# **Contents**

| Paragraph<br>Number | Title                                                 | Page<br>Number |

|---------------------|-------------------------------------------------------|----------------|

|                     | About This Book                                       |                |

|                     |                                                       | ::::           |

|                     | Audience                                              |                |

|                     | Organization                                          |                |

|                     | Suggested Reading                                     |                |

|                     | General Information                                   |                |

|                     | Related Documentation                                 |                |

|                     | Conventions                                           |                |

|                     | Signals                                               | i-xv           |

|                     | Chapter 1                                             |                |

|                     | Introduction                                          |                |

| 1.1                 | Overview                                              | 1-1            |

| 1.2                 | Features                                              | 1-2            |

| 1.3                 | Block Diagram                                         | 1-3            |

| 1.4                 | References                                            | 1-5            |

|                     | Chapter 2                                             |                |

|                     | Transmitter                                           |                |

| 2.1                 | Transmitter Block Diagram                             | 2-2            |

| 2.2                 | Transmitter Interface Signals                         |                |

| 2.3                 | Transmitter Interface Configuration                   |                |

| 2.3.1               | Transmit Driver Operation.                            |                |

| 2.3.2               | Repeater Mode Operation                               | 2-5            |

| 2.4                 | Backplane Application Modes (COMPAT = Low)            | 2-5            |

| 2.4.1               | Transmitting Uncoded Data—8-/4-Bit Modes              | 2-6            |

| 2.4.2               | Transmitting Coded Data—10-/5-Bit Modes               | 2-7            |

| 2.5                 | Ethernet Compliant Applications Modes (COMPAT = High) | 2-9            |

| 2.5.1               | Transmitting Uncoded Data—GMII or RGMII Modes         |                |

| 2.5.1.1             | Auto-Negotiation Process                              |                |

| 2.5.1.2             | Ethernet Data Transmission Process.                   |                |

| 2.5.2               | Transmitting Coded Data—TBI or RTBI Modes             |                |

| 2.6                 | Transmitter Redundant Link Operation                  | 2-12           |

Freescale Semiconductor iii

| Paragraph<br>Number | Title                                                 | Page<br>Number |

|---------------------|-------------------------------------------------------|----------------|

| Nullibei            |                                                       | Number         |

|                     | Chapter 3 Receiver                                    |                |

| 3.1                 | Receiver Block Diagram                                | 3-2            |

| 3.2                 | Receiver Interface Signals                            | 3-3            |

| 3.3                 | Functional Description.                               |                |

| 3.3.1               | Input Amplifier                                       |                |

| 3.3.2               | Transition Tracking Loop and Data Recovery            |                |

| 3.3.3               | 8B/10B Decoder                                        |                |

| 3.3.4               | Half-Speed Mode                                       | 3-6            |

| 3.3.5               | Repeater Mode                                         |                |

| 3.3.6               | Receiver Redundant Link Operation                     |                |

| 3.4                 | Receiver Interface Configuration                      |                |

| 3.5                 | Data Alignment Configurations                         |                |

| 3.5.1               | Non-Aligned Mode (BSYNC = Low)                        |                |

| 3.5.2               | Byte-Aligned Mode (BSYNC = High)                      |                |

| 3.5.3               | Word Synchronization                                  |                |

| 3.5.3.1             | Word Synchronization Method                           |                |

| 3.6                 | Receiver Interface Timing Modes.                      |                |

| 3.6.1               | Recovered Clock Timing Mode (RCCE = High)             |                |

| 3.6.2               | Reference Clock Timing Mode (RCCE = Low)              |                |

| 3.7                 | Ethernet Compliant Applications Modes (COMPAT = High) |                |

| 3.7.1               | Interface to Ethernet MAC                             |                |

| 3.7.1.1             | GMII Operation                                        |                |

| 3.7.1.2             | TBI Operation                                         |                |

| 3.7.1.3             | Double Data Rate Operation—RGMI and RTBI              |                |

| 3.7.2               | Rate Adaption of Ethernet Packet Data Streams         |                |

| 3.7.2.1             | Rate Adaption Method                                  | 3-17           |

| 3.7.2.2             | Configuration Context                                 | 3-17           |

| 3.7.2.3             | Idle Context                                          | 3-18           |

| 3.7.2.4             | Data Context                                          | 3-19           |

| 3.7.3               | Error Handling                                        | 3-19           |

| 3.7.3.1             | Jumbo Frame Considerations                            | 3-19           |

| 3.8                 | Backplane Applications Modes (COMPAT = Low)           | 3-20           |

| 3.8.1               | Byte Mode (Uncoded Data)                              |                |

| 3.8.2               | 10-Bit Mode (Coded Data)                              |                |

| 3.8.2.1             | Double Data Rate Operation—Backplane Applications     |                |

| Paragraph<br>Number | Title                                                                  | Page<br>Number |

|---------------------|------------------------------------------------------------------------|----------------|

|                     | Chapter 4                                                              |                |

|                     | Management Interface (MDIO)                                            |                |

| 4.1                 | MDIO Interface                                                         | 4-1            |

| 4.2                 | MDIO Registers                                                         |                |

| 4.2.1               | MDIO RA 0—Control Register                                             |                |

| 4.2.2               | MDIO RA 1—Status Register                                              |                |

| 4.2.3               | MDIO RA 2 and 3—PHY Identifier Registers                               |                |

| 4.2.4               | MDIO RA 4—Auto-Negotiation Advertisement Register                      |                |

| 4.2.5               | MDIO RA 5—Auto-Negotiation Link Partner Ability Register               |                |

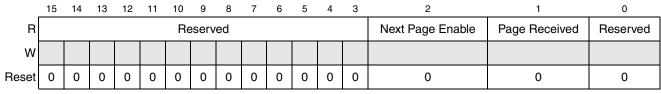

| 4.2.6               | MDIO RA 6—Auto-Negotiation (AN) Expansion Register                     | 4-8            |

| 4.2.7               | MDIO RA 7–14—Not Supported                                             | 4-8            |

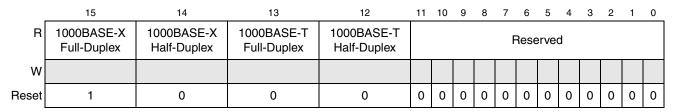

| 4.2.8               | MDIO RA 15—Extended Status Register                                    | 4-8            |

| 4.2.9               | MDIO RA 16 (Vendor Specific)—Permanent Configuration Control Register  | ·4-9           |

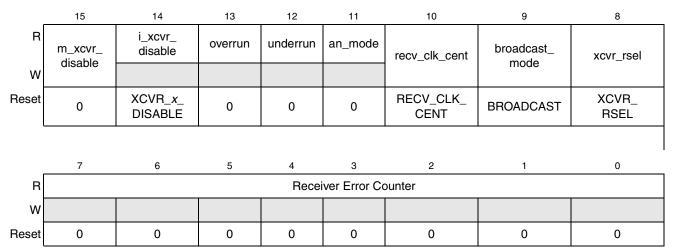

| 4.2.10              | MDIO RA 17 (Vendor Specific)—Channel Configuration and Status Register | r <b>4-</b> 11 |

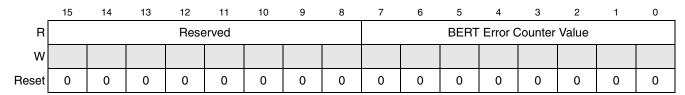

| 4.2.11              | MDIO RA 18 (Vendor Specific)—BERT Error Counter Register               | 4-12           |

|                     | Chapter 5                                                              |                |

| E 1                 | System Design Considerations                                           | <i>E</i> 1     |

| 5.1                 | Reference Clock Configuration                                          |                |

| 5.2                 | Startup                                                                |                |

| 5.3                 | Standby Mode                                                           |                |

| 5.4                 | Receiver Interface Clock Centering                                     |                |

| 5.5                 | Repeater Mode                                                          |                |

| 5.5.1               | Ten-Bit Interface Mode                                                 |                |

| 5.5.2               | Byte Alignment Mode                                                    |                |

| 5.5.3               | Word Synchronization Mode                                              |                |

| 5.5.4               | Recovered Clock Mode                                                   |                |

| 5.5.5               | Add/Drop Idle Mode                                                     |                |

| 5.5.6               | Half-Speed Mode                                                        |                |

| 5.6                 | Configuration and Control Signals                                      |                |

| 5.7                 | Power Supply Requirements                                              |                |

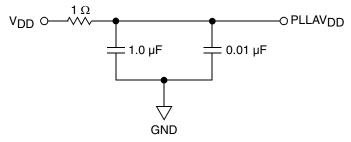

| 5.8                 | Phase-Locked Loop (PLL) Power Supply Filtering                         |                |

| 5.9                 | Power Supply Decoupling Recommendations                                | 5-7            |

Freescale Semiconductor

| Paragraph<br>Number | Title                                                            | Page<br>Number |

|---------------------|------------------------------------------------------------------|----------------|

|                     | Chapter 6                                                        |                |

|                     | Test Features                                                    |                |

| 6.1                 | IEEE Std. 1149.1 Implementation                                  | 6-1            |

| 6.1.1               | Test Access Port (TAP) Interface Signals                         |                |

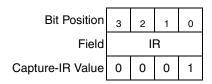

| 6.1.2               | Instruction Register                                             |                |

| 6.1.3               | Instructions                                                     | 6-2            |

| 6.1.4               | Boundary Scan Register                                           | 6-2            |

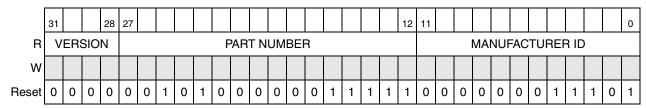

| 6.1.5               | Device Identification Register (0x0281F01D)                      | 6-3            |

| 6.1.6               | Performance                                                      | 6-3            |

| 6.2                 | System Accessible Test Modes                                     | 6-3            |

| 6.2.1               | Loopback System Test                                             |                |

| 6.2.2               | BIST Sequence System Test with External Loopback Modes           | 6-4            |

| 6.3                 | BIST Sequence Test with Internal Digital Loopback Mode           |                |

|                     | Chapter 7                                                        |                |

|                     | Electrical Specifications and Characteristics                    |                |

| 7.1                 | General Characteristics                                          | 7-1            |

| 7.1.1               | General Parameters                                               | 7-1            |

| 7.1.2               | Absolute Maximum Rating                                          | 7-2            |

| 7.1.3               | Recommended Operating Conditions                                 | 7-2            |

| 7.2                 | DC Electrical Specifications                                     | 7-3            |

| 7.3                 | AC Electrical Characteristics                                    | 7-4            |

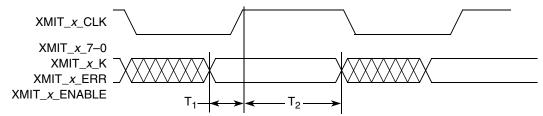

| 7.3.1               | Transmitter Interface Timing                                     | 7-4            |

| 7.3.1.1             | Transmitter Interface, Non-DDR Timing                            | 7-4            |

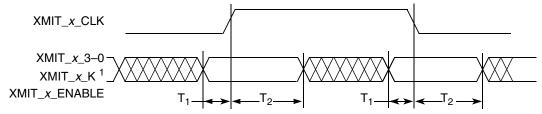

| 7.3.1.2             | Transmitter Interface, DDR Timing                                | 7-5            |

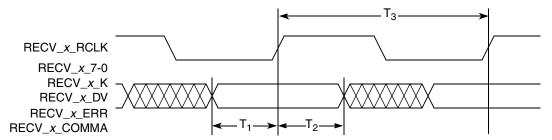

| 7.3.2               | Receiver Interface Timing                                        | 7-6            |

| 7.3.2.1             | Receiver Interface, Non-DDR Timing                               | 7-7            |

| 7.3.2.1.1           | Receiver, Non-DDR Clock Timing (All Modes Except Ethernet TBI Mo | des) 7-7       |

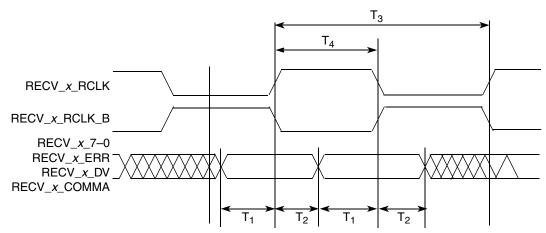

| 7.3.2.1.2           | Receiver Interface, Non-DDR Clock Timing (Ethernet TBI Mode)     | 7-8            |

| 7.3.2.2             | Receiver Interface, DDR Timing.                                  | 7-9            |

| 7.3.2.2.1           | Receiver, DDR Clock Timing (All Modes Except Ethernet RTBI Modes | ) 7-9          |

| 7.3.2.2.2           | Receiver, DDR Clock Timing (Ethernet RTBI Mode)                  |                |

| 7.3.3               | Reference Clock Timing                                           |                |

| 7.3.4               | Serial Data Link Timing                                          |                |

| 7.3.5               | MDIO Interface Timing                                            |                |

| 7.3.6               | JTAG Test Port Timing                                            | 7-14           |

vi Freescale Semiconductor

| Paragraph<br>Number | Title                                                 | Pag<br>Numbe |  |

|---------------------|-------------------------------------------------------|--------------|--|

|                     | Chapter 8                                             |              |  |

|                     | Package Description                                   |              |  |

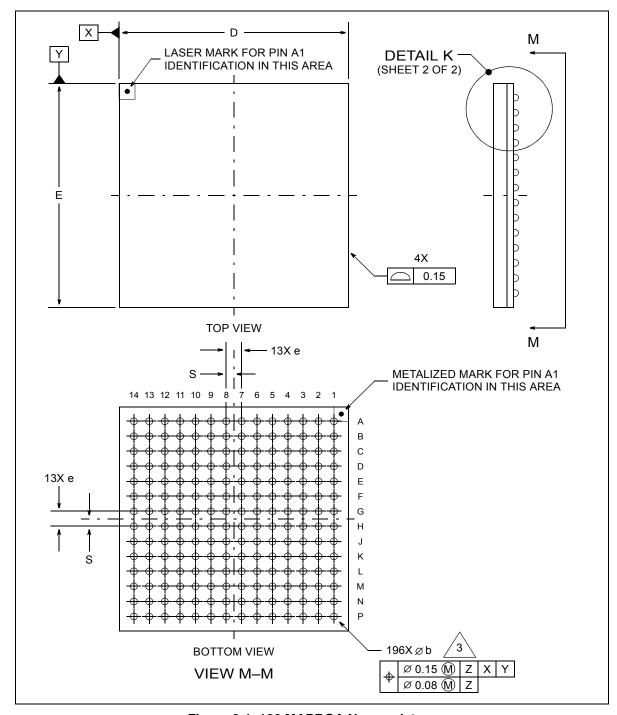

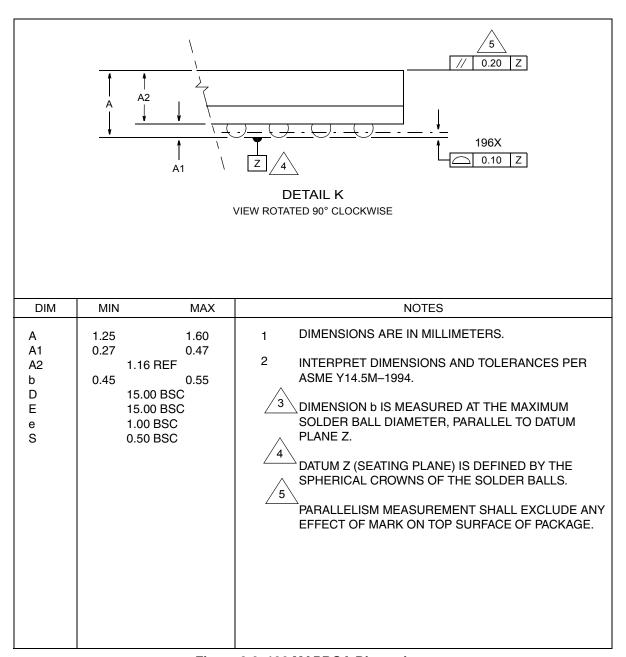

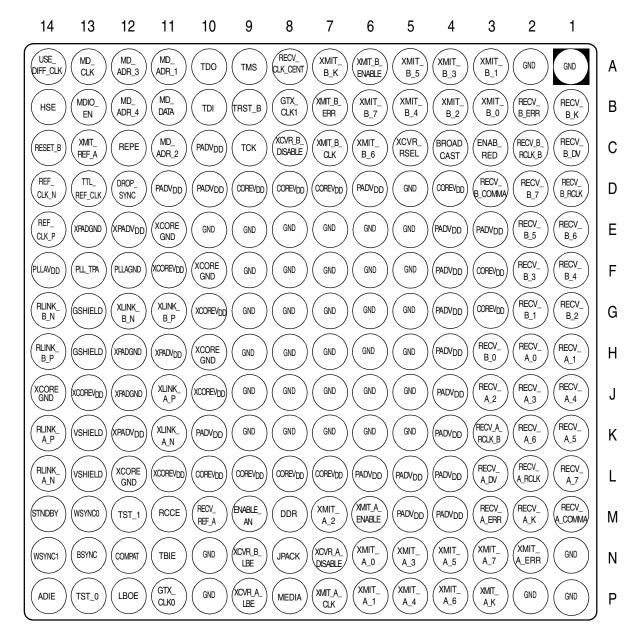

| 8.1                 | 196 MAPBGA Package Parameter Summary                  | 8-1          |  |

| 8.2                 | Nomenclature and Dimensions of the 196 MAPBGA Package | 8-1          |  |

| 8.3                 | Package Thermal Characteristics                       | 8-5          |  |

| 8.4                 | MC92604 Chip Pinout Listing                           | 8-5          |  |

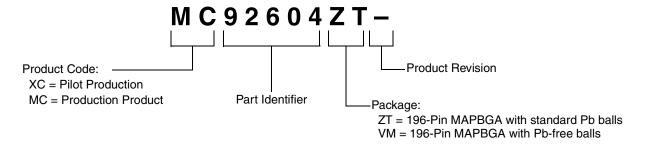

|                     | Appendix A Ordering Information                       |              |  |

|                     | Appendix B<br>8B/10B Coding Scheme                    |              |  |

| B.1                 | Overview                                              | B-1          |  |

| B.1.1               | Naming Transmission Characters                        | B-2          |  |

| B.1.2               | Encoding                                              | B-2          |  |

| B.1.3               | Calculating Running Disparity                         | B-3          |  |

| B.2                 | Data Tables                                           | B-3          |  |

|                     | Appendix C                                            |              |  |

Appendix C Revision History

**Glossary of Terms and Abbreviations**

Index

MC92604 Dual Gigabit Ethernet Transceiver Reference Manual, Rev. 1

Freescale Semiconductor vii

MC92604 Dual Gigabit Ethernet Transceiver Reference Manual, Rev. 1

viii Freescale Semiconductor

# **Figures**

| Figure<br>Number | Title                                                            | Page<br>Number |

|------------------|------------------------------------------------------------------|----------------|

| 1-1              | MC92604 Simplified Block Diagram                                 | 1-3            |

| 1-2              | MC92604 Block Diagram                                            | 1-4            |

| 1-3              | PHY and Backplane Applications                                   | 1-5            |

| 2-1              | MC92604 Transmitter Block Diagram                                | 2-2            |

| 2-2              | Configuration Register                                           | 2-10           |

| 3-1              | MC92604 Receiver Block Diagram                                   | 3-2            |

| 4-1              | Control Register (MDIO RA 0)                                     | 4-3            |

| 4-2              | Status Register (MDIO RA 1)                                      | 4-4            |

| 4-3              | PHY Identifier Registers (MDIO RA 2 and 3)                       | 4-5            |

| 4-4              | Auto-Negotiation (AN) Advertisement Register (MDIO RA 4)         | 4-6            |

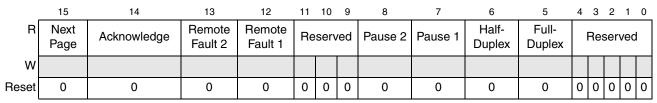

| 4-5              | AN Link Partner Ability Register (MDIO RA 5)                     | 4-7            |

| 4-6              | AN Expansion Register (MDIO RA 6)                                | 4-8            |

| 4-7              | Extended Status Register (MDIO RA 15)                            | 4-8            |

| 4-8              | Permanent Configuration Control Register (MDIO RA 16)            | 4-9            |

| 4-9              | Channel Configuration and Status Register (MDIO RA 17)           | 4-11           |

| 4-10             | BERT Error Counter Register (MDIO RA 18)                         | 4-12           |

| 5-1              | PLL Power Supply Filter Circuits                                 | 5-6            |

| 6-1              | Instruction Register                                             | 6-2            |

| 6-2              | Device Identification Register                                   | 6-3            |

| 7-1              | Transmitter Interface, Non-DDR Timing Diagram                    | 7-4            |

| 7-2              | Transmitter Interface, DDR Timing Diagram                        | 7-5            |

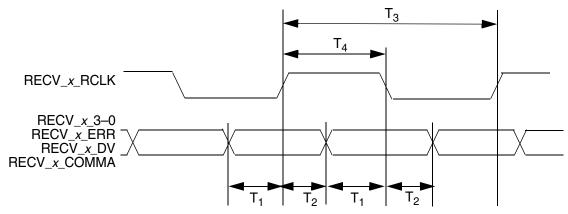

| 7-3              | Receiver, Non-DDR Timing Diagram (TBIE = Low or COMPAT = Low)    | 7-7            |

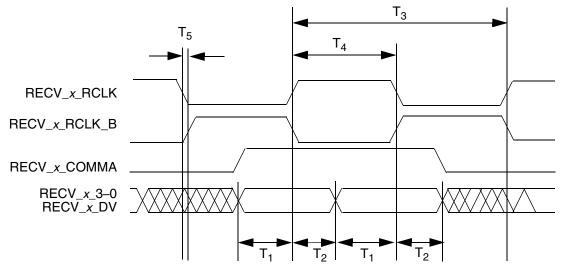

| 7-4              | Receiver, Non-DDR Timing Diagram (TBIE = High and COMPAT = High) | 7-8            |

| 7-5              | Receiver, DDR Timing Diagram (TBIE = Low or COMPAT = Low)        | 7-9            |

| 7-6              | Receiver, DDR Timing Diagram (TBIE = High and COMPAT = High)     | 7-10           |

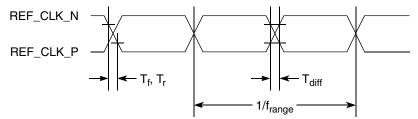

| 7-7              | Reference Clock Timing Diagram                                   |                |

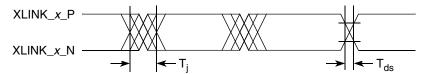

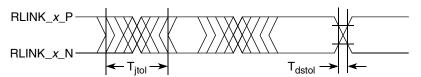

| 7-8              | Link Differential Output Timing Diagram                          | 7-12           |

| 7-9              | Link Differential Input Timing Diagram                           | 7-12           |

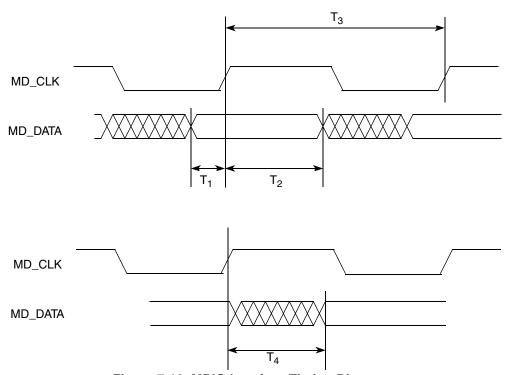

| 7-10             | MDIO Interface Timing Diagram                                    | 7-13           |

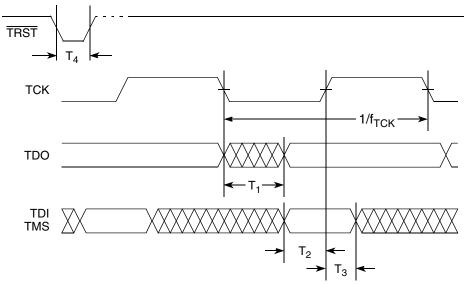

| 7-11             | JTAG I/O Timing Diagram                                          |                |

| 8-1              | 196 MAPBGA Nomenclature                                          | 8-2            |

| 8-2              | 196 MAPBGA Dimensions                                            | 8-3            |

| 8-3              | MC92604 Package Ball Mapping                                     | 8-4            |

| <b>A-1</b>       | Freescale Part Number Key                                        |                |

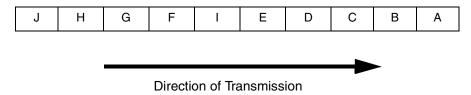

| B-1              | Unencoded Transmission Character Bit Ordering                    |                |

| B-2              | Encoded Transmission Character Bit Ordering                      |                |

| B-3              | Character Transmission                                           | B-2            |

x Freescale Semiconductor

# **Tables**

| Table<br>Number | Title                                                               | Page<br>Number |

|-----------------|---------------------------------------------------------------------|----------------|

| 2-1             | MC92604 Transmitter Interface Signals                               | 2-3            |

| 2-2             | MC92604 Data Interface Modes                                        | 2-4            |

| 2-3             | Transmitter Control States for Uncoded Data (TBIE = Low)            | 2-6            |

| 2-4             | Transmitter Inputs for Reduced Uncoded Data—Backplane Mode          | 2-7            |

| 2-5             | Transmitter Input States for Coded Data (TBIE = High)               | 2-7            |

| 2-6             | Transmitter Inputs for RTBI Operating Mode                          | 2-8            |

| 2-7             | Gigabit Ethernet Defined Ordered Sets                               | 2-9            |

| 2-8             | Transmitter Inputs for RGMII Operating Mode                         | 2-11           |

| 2-9             | Transmit Redundant Link Operation                                   | 2-12           |

| 3-1             | MC92604 Receiver Interface Signals                                  | 3-3            |

| 3-2             | Receiver Redundant Link Operation.                                  |                |

| 3-3             | MC92604 Receiver Operating Modes (Common Features/Characteristics)  | 3-7            |

| 3-4             | Byte Synchronization Modes                                          |                |

| 3-5             | Word Synchronization Events                                         | 3-10           |

| 3-6             | Receiver Reference Clock is Slower than Transmitter Reference Clock |                |

| 3-7             | Receiver Reference Clock is Faster than Transmitter Reference Clock |                |

| 3-8             | GMII Connection to Standard Ethernet MAC                            | 3-14           |

| 3-9             | Receiver Status in GMII Mode                                        |                |

| 3-10            | TBI Connection to Standard Ethernet MAC                             |                |

| 3-11            | Receiver Interface Error and Status Codes (TBI Mode)                |                |

| 3-12            | Receiver RGMII Interface                                            |                |

| 3-13            | Receiver RTBI Interface                                             |                |

| 3-14            | Receiver Interface Error and Status Codes (Backplane Byte Mode)     |                |

| 3-15            | Receiver Interface Error and Status Codes (Backplane 10-Bit Mode)   |                |

| 3-16            | DDR Backplane Uncoded Data (8-Bit Mode)                             |                |

| 3-17            | DDR Backplane Coded Data (10-Bit Mode)                              |                |

| 4-1             | MDIO Management Register Set.                                       |                |

| 4-2             | Control Register (MDIO RA 0) Field Descriptions                     |                |

| 4-3             | Status Register (MDIO RA 1) Field Descriptions                      |                |

| 4-4             | AN Advertisement Register (MDIO RA 4) Field Descriptions            |                |

| 4-5             | AN Link Partner Ability Register Field Descriptions                 |                |

| 4-6             | Permanent Configuration Control Register Field Descriptions         |                |

| 4-7             | Channel Configuration and Status Register Field Descriptions        |                |

| 5-1             | Legal Reference Clock Frequency Ranges                              |                |

| 5-2             | Startup Sequence Step Duration                                      |                |

| 5-3             | Asynchronous Configuration and Control Signals                      | 5-5            |

| Table<br>Number | Title                                                                    | Page<br>Number |

|-----------------|--------------------------------------------------------------------------|----------------|

| 6-1             | TAP Interface Signals                                                    | 6-1            |

| 6-2             | Tap Controller Public Instructions                                       | 6-2            |

| 6-3             | Tap Controller Private Instruction Codes.                                | 6-2            |

| 6-4             | Test Mode State Selection                                                | 6-3            |

| 6-5             | BIST Error Codes.                                                        | 6-5            |

| 7-1             | Absolute Maximum Ratings                                                 | 7-2            |

| 7-2             | Recommended Operating Conditions                                         | 7-2            |

| 7-3             | DC Electrical Specifications                                             | 7-3            |

| 7-4             | Transmitter Non-DDR Timing Specification                                 | 7-4            |

| 7-5             | Transmitter DDR Timing Specifications                                    | 7-5            |

| 7-6             | Target Receiver Clock Offset Relative to Data                            | 7 <b>-</b> 6   |

| 7-7             | Receiver, Non-DDR Timing Specifications (TBIE = Low or COMPAT = Low)     | 7-7            |

| 7-8             | Receiver, Non-DDR Timing Specifications (TBIE = High and COMPAT = High). | 7-8            |

| 7-9             | Receiver, DDR Timing Specification (TBIE = Low or COMPAT = Low)          | 7 <b>-</b> 9   |

| 7-10            | Receiver, DDR Timing Specification (TBIE = High and COMPAT = High)       | 7-10           |

| 7-11            | Reference Clock Specifications                                           | 7-11           |

| 7-12            | Link Differential Output Specifications                                  | 7-12           |

| 7-13            | Link Differential Input Timing Specifications                            | 7-12           |

| 7-14            | MDIO Interface Timing Specifications                                     | 7-13           |

| 7-15            | JTAG I/O Timing Specifications                                           | 7-14           |

| 8-1             | MC62604 Package Thermal Resistance Values                                | 8-5            |

| 8-2             | MC92604 Signal to Ball Mapping                                           | 8-5            |

| B-1             | Components of a Character Name                                           | B-2            |

| B-2             | Valid Data Characters.                                                   | B-4            |

| B-3             | Valid Special Characters                                                 | B-8            |

| C-1             | Revision History Table                                                   | C-1            |

# **About This Book**

The primary objective of this reference manual is to describe the functionality of the MC92604 for software and hardware developers.

Information in this book is subject to change without notice, as described in the disclaimers on the title page of this book. As with any technical documentation, it is the readers' responsibility to be sure they are using the most recent version of the documentation.

### **Audience**

It is assumed that the reader has the appropriate general knowledge regarding the design and layout requirements for high-speed (Gbps) digital signaling and understanding of the basic principles of the Ethernet and Fibre Channel communications protocols to use the information in this manual.

# **Organization**

The following is a summary and a brief description of the major chapters in this manual:

- Chapter 1, "Introduction," gives an overview of the device features and shows a block diagram of the major functional blocks of the part.

- Chapter 2, "Transmitter," describes the MC92604 transmitter, its interfaces, and operational options.

- Chapter 3, "Receiver," gives a description of the receiver, its interfaces, and operation.

- Chapter 4, "Management Interface (MDIO)," describes the MDIO interface signals and the associated registers.

- Chapter 5, "System Design Considerations," describes the system considerations for the MC92604, including clock configuration, device startup and initialization, and proper use of the configuration control signals.

- Chapter 6, "Test Features," covers the JTAG implementation and the system accessible test modes.

- Chapter 7, "Electrical Specifications and Characteristics," describes the DC and AC electrical characteristics.

- Chapter 8, "Package Description," provides the package parameters and mechanical dimensions and signal pin to ball mapping tables for the MC92604 device.

- Appendix A, "Ordering Information," provides the Freescale part numbering nomenclature for the MC92604 transceiver.

- Appendix B, "8B/10B Coding Scheme," provides tables of the fibre channel-specific 8B/10B encoding and decoding as based on the ANSI FC-1 fibre channel standard.

Freescale Semiconductor xiii

- Appendix C, "Revision History," lists the major differences between revisions of this book, the *MC92604 Dual Gigabit Ethernet Transceiver Reference Manual* (MC92604RM).

- "Glossary of Terms and Abbreviations," contains an alphabetical list of terms, phrases, and abbreviations used in this book.

- "Index," contains all general entries for the book.

# **Suggested Reading**

This section lists additional reading that provides background for the information in this manual as well as general information about the architecture.

### **General Information**

The following documentation, published by Morgan-Kaufmann Publishers, 340 Pine Street, Sixth Floor, San Francisco, CA, provides useful information about the PowerPC<sup>TM</sup> architecture and computer architecture in general:

- The PowerPC Architecture: A Specification for a New Family of RISC Processors, Second Edition, by International Business Machines, Inc.

- Computer Architecture: A Quantitative Approach, Second Edition, by John L. Hennessy and David A. Patterson

- Computer Organization and Design: The Hardware/Software Interface, Second Edition, David A. Patterson and John L. Hennessy

### **Related Documentation**

Freescale documentation is available from the sources listed on the back cover of this book; the document order numbers are included in parentheses for ease in ordering:

- Reference manuals—These books provide details about individual device implementations. The *MC92604DVB Dual GEt Design Verification Board User's Guide* (MC92604DVBUG) describes how to use the design verification board and should be read in conjunction with this book, the *MC92604 Dual Gigabit Ethernet Transceiver Reference Manual* (MC92604RM).

- Addenda/errata to reference manuals—Because some devices have follow-on parts an addendum provides any additional features and functionality changes. These addenda are intended for use with the corresponding reference manuals.

- Hardware specifications—Hardware specifications provide specific data regarding bus timing, signal behavior, and AC, DC, and thermal characteristics, as well as other design considerations. This manual contains all the hardware specifications for the MC92604.

- Application notes—These short documents address specific design issues useful to programmers and engineers working with Freescale devices.

- White papers—These documents provide detail on a specific design platform and are useful to programmers and engineers working on a specific product. The MC92610 3.125 Gbaud Reference Design Platform (BR1570) describes the technical design process used in developing a high-speed backplane reference design.

MC92604 Dual Gigabit Ethernet Transceiver Reference Manual, Rev. 1

xiv Freescale Semiconductor

• Additional literature is published as new processors become available. For a current list of documentation, refer to <a href="http://www.freescale.com">http://www.freescale.com</a>.

### **Conventions**

This document uses the following notational conventions:

Book titles in text are set in italics

Internal signals are set in italics, for example, *loopback\_data*

- \* Notation for multiplication

- Ox Prefix to denote hexadecimal number

- Ob Prefix to denote binary number

- x In some contexts, such as signal encodings, an un-italicized x indicates a don't care.

- x An italicized x indicates an alphanumeric variable.

- *n* An italicized *n* indicates a numeric variable.

# **Signals**

A bar over a signal name indicates that the signal is active low—for example, RESET and TRST. Active low signals are referred to as asserted (active) when they are low and negated when they are high. Signals that are not active low, such as XMIT\_A\_ENABLE and DROP\_SYNC, are referred to as asserted when they are high and negated when they are low.

Freescale Semiconductor xv

MC92604 Dual Gigabit Ethernet Transceiver Reference Manual, Rev. 1

xvi Freescale Semiconductor

# Chapter 1 Introduction

This chapter consists of the following sections:

- Section 1.1, "Overview"

- Section 1.2, "Features"

- Section 1.3, "Block Diagram"

- Section 1.4, "References"

This reference manual explains the functionality of the MC92604 Dual transceivers (GEt) and enables its use by software and hardware developers. The audience for this publication, therefore, consists of hardware designers and application programmers who are building data path switches and high-speed backplane intercommunication applications.

#### 1.1 Overview

The Gigabit Ethernet transceiver was designed with the intent to meet the requirements of **IEEE Std. 802.3—2002**<sup>®</sup>. It was designed to fully support full-duplex GMII or TBI PHY applications including the reduced RGMII or RTBI defacto interfaces. Each channel also has its own independent MDIO register set as specified in the above standard.

The MC92604 GEt is designed as four parts in one. It may be configured as either a 1 Gigabit backplane serializer/deserializer (SerDes) with functionally similar to the *1.25 Gbaud Quad SerDes* (MC92600), or as a Dual 1 Gigabit Ethernet PHY and the reduced interface versions of these two.

The GEt is a high-speed, full-duplex, serial data interface device that can be used to transmit data between chips across a board, through a backplane, or through cabling, as well as to interface to GBIC/SFP modules. The multi-channel device has transceivers that transmit and receive coded data at a rate of 1.0 Gbps through each 1.25 gigabaud link.

The MC92604 is built on the proven transceiver technology of the MC92600 and MC92602 devices. Carefully designed for low-power consumption, its CMOS implementation nominally consumes less than 1 W with all links operating at full speed when in the backplane interface mode.

The MC92604 features transmit FIFOs and source synchronous transmit clocks per channel to further simplify interfacing. Additionally, **IEEE Std 1149.1—1990**<sup>TM</sup> JTAG boundary scan and built-in PRBS generator/analyzers are provided for board test support.

Freescale Semiconductor 1-1

#### 1.2 Features

The MC92604 has two applications-oriented operating modes depending on the configuration. It may be used as a backplane SerDes or an Ethernet PHY.

The main features of the MC92604 are as follows:

- Common features:

- Two independent SerDes channels with full-duplex differential data links

- Configurable as a single channel device to provide redundant transmit and receive serial links

- Selectable speed range: 1.25 or 0.625 Gbaud

- Internal 8B/10B encoder/decoder that may be bypassed

- Source synchronous parallel data input interfaces

- Selectable: source-aligned or source-centered timing on the receiver output interfaces

- DDR (RGMII/RTBI), source synchronous, 4-/5-bit optional interfaces

- Parallel interfaces may be either 2.5- or 3.3-V LVTTL. Device will inter-operate with SSTL\_2 with the 2.5-V LVTTL interface.

- Transmit data clock is selectable between per-channel transmit clock or channel 'A' transmit clock

- Received data may be clocked to the reference clock or to the received data frequencies

- Unused transceiver channel may be disabled

- Drives 50- or 75- $\Omega$  media (100- or 150- $\Omega$  differential) for lengths of up to 1.5 meters board/backplane, or 10 meters of coax.

- Tolerates a  $\pm 250$  ppm frequency offset between the transmitter and receiver

- Link inputs have on-chip receiver termination and are 'hot swap' compatible

- Low power (less than 0.6 W) under typical conditions while operating in backplane mode with all transceivers at full speed

- Differential LVPECL reference clock input with single-ended LVCMOS input option

- Two single-ended buffered reference clock outputs to be used as the clock source for associated MAC interface logic.

- Built-in, at speed, self test for production testing and on-board diagnostics

- IEEE Std. 1149.1 JTAG boundary scan test support

- Backplane application features:

- Link-to-link synchronization supports aligned, multi-channel word transfers. Synchronization mechanism tolerates up to 40 bit-times of link-to-link media delay skew.

- Supports disparity-based word sync events for compatibility with legacy transceivers

- Selectable COMMA code group alignment mode enables aligned or unaligned transfers

- Ethernet friendly features:

- GMII, TBI, RGMII, or RTBI data interface options

- COMMA code group alignment in receivers

- Provides the PCS and PMA layers for Ethernet PHYs as specified in IEEE Std. 802.3-2000

- MDIO slave interface and registers as defined in IEEE Std. 802.3-2002 are fully supported

- Supports rate adaption within IPG for jumbo frames up to 14 Kbytes

1-2 Freescale Semiconductor

### 1.3 Block Diagram

The MC92604 is a highly integrated device containing all of the logic needed to facilitate the application and testing of a high-speed serial interface. No external components, other than the normal power supply decoupling network, are required.

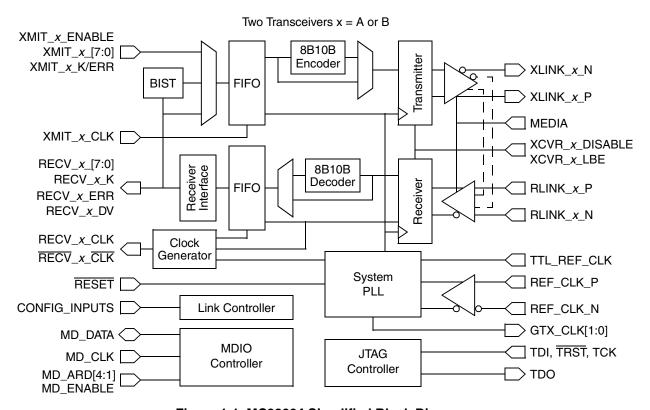

A simplified block diagram of the MC92604 device is shown in Figure 1-1, and a full block diagram is provided in Figure 1-2.

Figure 1-1. MC92604 Simplified Block Diagram

Freescale Semiconductor 1-3

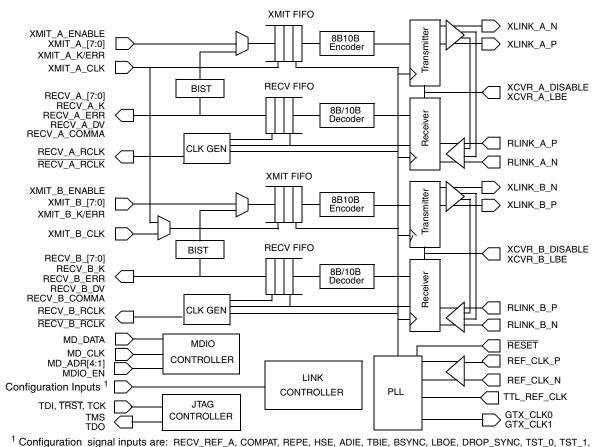

WSYNC0, WSYNC1, STNDBY, XMIT\_REF\_A, MEDIA, RCCE, JPACK, RECV\_CLK\_CENT, DDR, ENABLE\_AN, USE\_DIFF\_CLK, ENAB\_RED, BROADCAST, XCVR\_RSEL

Figure 1-2. MC92604 Block Diagram

The MC92604 performs the physical coding sublayer (PCS) and the physical medium attachment (PMA) sublayer for 1000BASE-X PHY as defined in clause 36 of the IEEE Std. 802.3-2002 specification [4].

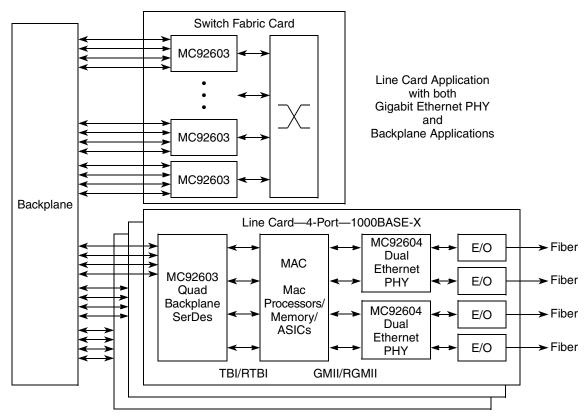

Figure 1-3 shows a typical application for the MC92604 which may be used as a dual1000BASE-X PHY or in backplane applications. On high density line cards with a large number of Gig-Ethernet ports, it is desirable to use the RGMII interfaces to reduce the number of signal traces on the PCB.

The MC92604 may be used to interface directly to the Gigabit MACs integrated into the MPC PowerQUICC III<sup>TM</sup> communications processors. They are also interface-compatible to C-Port's C-3 and C-5 network processors available from Freescale.

1-4 Freescale Semiconductor

Figure 1-3. PHY and Backplane Applications

### 1.4 References

The indexed references in this manual are as follows:

- [1] Fibre Channel, Gigabit Communications and I/O for Computer Networks, Brenner, 1996.

- [2] Byte Oriented DC Balanced 8B/10B Partitioned Block Transmission Code, U.S. Patent #4,486,739, Dec. 4, 1984.

- [3] IEEE Standard Test Access Port and Boundary-Scan Architecture, IEEE Std. 1149.1-1990 (includes IEEE Std. 1149.1a-1993), Oct. 1993.

- [4] IEEE Standard Carrier Sense Multiple-Access with Collision Detection (CSMA/CD) Access Method and Physical Layer Specifications, IEEE Std. 802.3-2002, March 2002.

Introduction

MC92604 Dual Gigabit Ethernet Transceiver Reference Manual, Rev. 1

1-6 Freescale Semiconductor

## **Chapter 2 Transmitter**

This chapter describes the MC92604 transmitter and its interfaces and operation. This chapter consists of the following sections:

- Section 2.1, "Transmitter Block Diagram"

- Section 2.2, "Transmitter Interface Signals"

- Section 2.3, "Transmitter Interface Configuration"

- Section 2.4, "Backplane Application Modes (COMPAT = Low)"

- Section 2.5, "Ethernet Compliant Applications Modes (COMPAT = High)"

- Section 2.6, "Transmitter Redundant Link Operation"

The MC92604 is a versatile device that may be used in backplane SerDes or Ethernet PHY applications. It may be configured in multiple data interface and operational modes. The following sections provide a basic functional description of the transmitter, its operational modes, and data interfaces. Each transmitter takes data presented at its source synchronous parallel data input port, creates a transmission code group or character (if not pre-encoded), and serially transmits the code group out of the differential link output pads.

Freescale Semiconductor 2-1

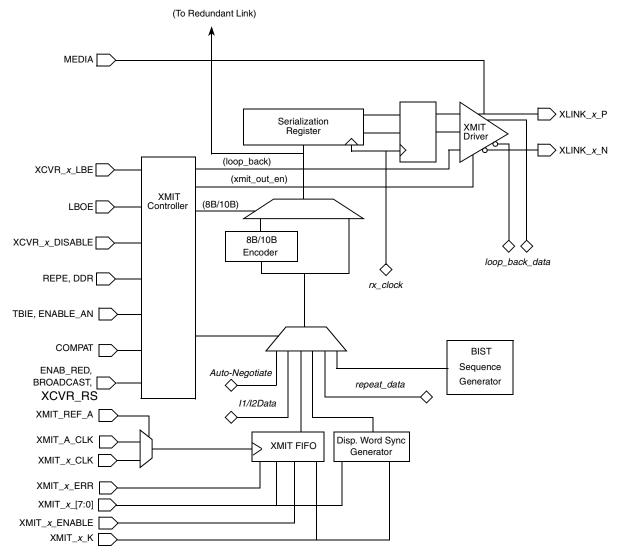

#### **Transmitter Block Diagram** 2.1

Figure 2-1 shows a block diagram of the MC92604 transmitter.

Figure 2-1. MC92604 Transmitter Block Diagram

#### 2.2 **Transmitter Interface Signals**

This section describes the interface signals of the MC92604 transmitters. Each signal's name, function, direction, and active state is described in Table 2-1. The table's signal names use the letter 'x' as a place holder for the link identifier letter 'A' or 'B.' Internal signals listed in the table are not available at the external interface of the device but are presented to help illustrate the device's operation.

MC92604 Dual Gigabit Ethernet Transceiver Reference Manual, Rev. 1 2-2 Freescale Semiconductor

Table 2-1. MC92604 Transmitter Interface Signals

| Signal Name    | Description                               | Function                                                                                                                                                                                                                                                      | Direction | Active<br>State |

|----------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------|

| XMIT_x_CLK     | Channel transmit clock                    | Clock input for each channel                                                                                                                                                                                                                                  | Input     | _               |

| XMIT_x_[7:0]   | Transmit data byte                        | 8 bits of transmit data                                                                                                                                                                                                                                       | Input     | _               |

| XMIT_x_K       | Transmit control/data bit                 | If TBIE is high, this input is used by the receiver to enable COMMA realignment. If TBIE and COMPAT are low, this is the 'K' (special character) input.                                                                                                       | Input     | _               |

| XMIT_x_ERR     | Transmit control/data bit                 | If TBIE is high, this is data bit 9. If TBIE and COMPAT are negated low, this is the 'force code error' input. If TBIE is low and COMPAT is high, this input is used as defined for GMII functionality (as defined in IEEE Std. 802.3-2002 specification[4]). | Input     | _               |

| XMIT_x_ENABLE  | Transmit enable data                      | If TBIE is high, this is data bit 8. If TBIE is low, this input defines transmit data is available on input.                                                                                                                                                  | Input     | High            |

| XCVR_x_LBE     | Loopback enable                           | Activate digital loopback path, such that data transmitted is looped back to corresponding receiver.                                                                                                                                                          | Input     | High            |

| XCVR_x_DISABLE | Transceiver disable                       | When active this transmitter is disabled.                                                                                                                                                                                                                     | Input     | High            |

| XMIT_REF_A     | Transmit interface clock select           | Indicates that the transmit interface signals are timed to XMIT_A_CLK instead of individual channel transmit clock.                                                                                                                                           | Input     | High            |

| LBOE           | Loopback output enable                    | If LBOE is high, link outputs remain active during digital loopback.  If LBOE is low, link outputs are disabled during loopback.                                                                                                                              | Input     | High            |

| REPE           | Repeater mode enable                      | When this input is high, data received on the corresponding receiver is 'repeated' by the transmitter.                                                                                                                                                        | Input     | High            |

| TBIE           | Ten-bit interface enable                  | Indicates that coded data is on the inputs, bypassing the internal 8B/10B coding.                                                                                                                                                                             | Input     | High            |

| COMPAT         | Enable IEEE Std.<br>802.3-2002 compliance | When enabled, transmitter conforms to IEEE Std. 802.3-2002 [4] GMII or TBI operating modes.                                                                                                                                                                   | Input     | High            |

| DDR            | Enable double data rate                   | When enabled the transmitter accepts 4/5 bits of data on positive edge of XMIT_x_CLK and the second 4/5 bits of data on the negative edge.                                                                                                                    | Input     | High            |

| ENABLE_AN      | Enable auto-negotiate                     | Allows the transceiver to perform an auto-negotiate sequence if in GMII mode (COMPAT high, TBIE low)                                                                                                                                                          | Input     | High            |

| ENAB_RED       | Enable redundant link                     | Enable redundant link operation. Channels A and B available to use with redundant links.                                                                                                                                                                      | Input     | High            |

| BROADCAST      | Transmit on both redundant links          | Broadcast transmitted data on both of the redundant links for each channel.                                                                                                                                                                                   | Input     | High            |

| XCVR_RSEL      | Select redundant link                     | Transmit data on the secondary (redundant) link                                                                                                                                                                                                               | Input     | High            |

Freescale Semiconductor 2-3

**Transmitter**

Table 2-1. MC92604 Transmitter Interface Signals (continued)

| Signal Name             | Description                  | Function                                                                                                      | Direction | Active<br>State |

|-------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------|-----------|-----------------|

| TST_1, TST_0            | Test mode config inputs      | Decoded to define various test modes (see<br>Chapter 6, "Test Features," for details)                         | Input     | _               |

| MEDIA                   | Media impedance select       | Indicates the impedance of the transmission media. Low indicates 50 $\Omega$ and high indicates 75 $\Omega$ . | Input     | _               |

| XLINK_x_N/<br>XLINK_x_P | Link serial transmit data    | ta Differential serial transmit data output pads                                                              | Output    | _               |

|                         | •                            | Internal Signals                                                                                              |           |                 |

| rx_clock                | High-speed transceiver clock | Internal, differential high speed clock used to transmit and receive link data                                | Input     | _               |

| repeat_data             | Received repeat data         | Repeater mode, received data to re-transmit                                                                   | Input     | _               |

| loop_back_data          | Loopback data                | Differential loopback transmit data                                                                           | Output    | _               |

| auto_neg_enable         | Auto-negotiation enable      | Auto-negotiate is enabled if this signal is high and in GMII mode                                             | Input     | High            |

### 2.3 Transmitter Interface Configuration

The transmitter may operate in one of eight data interface configurations as shown in Table 2-2. The compatibility configuration pin, COMPAT, establishes operation in either the backplane applications mode or the Ethernet compatible mode. The 10-bit interface enable, TBIE, configuration input, determines if the internal 8B/10B encoder will be used with uncoded input data or bypassed for a pre-encoded (coded) input data. When the DDR configuration pin is enabled, it reduces the interface from an 8-/10-bit single data rate interface to a 4-/5-bit double data rate interface.

The configuration signals, COMPAT and TBIE, also affect the receiver's configuration.

**Data Interface Mode COMPAT TBIE DDR** Backplane 8-bit uncoded data Low Low Low Backplane (4-bit reduced interface) uncoded data Low Low High Backplane 10-bit coded data Low High Low Backplane (5-bit reduced interface) coded data Low High High Ethernet compatible GMII High Low Low Ethernet compatible RGMII High Low High Ethernet compatible TBI High Low High Ethernet compatible RTBI High High High

Table 2-2. MC92604 Data Interface Modes

Transmit data is sampled and stored in the input FIFO on the rising edge (single data rate) of the appropriate transmit clock, if DDR is low, or both edges (double data rate) of the transmit clock if DDR is high. The FIFO accepts data to be transmitted and synchronizes it to the internal clock domain.

The 8B/10B encoder takes an 8-bit data/control from the input register and encodes it into 10-bit transmission characters. The fibre channel 8B/10B coding standard is followed [1,2]. A detailed

MC92604 Dual Gigabit Ethernet Transceiver Reference Manual, Rev. 1

2-4 Freescale Semiconductor

explanation of the 8B/10B coding scheme is offered in Appendix B, "8B/10B Coding Scheme." Running disparity is maintained, and the appropriate transmission characters are produced, maintaining DC balance and sufficient transition density to allow reliable data recovery at the receiver. The 8B/10B encoder is bypassed if TBIE is asserted high.

The transmitter data interface operates at high frequency (nominally 125 MHz). In order to ease development of devices that interface with the Gigabit Ethernet transceiver, all transmitter data input interfaces are source-synchronous. The data for each channel has its own dedicated clock input. This allows the clock at the source of the data to be routed with the data ensuring matched delay and timing. However, if per-channel clock sources are not available or deemed unnecessary, all channels may be clocked by a common clock source. This is enabled by asserting XMIT REF A high. When XMIT REF A is high, the XMIT A CLK becomes the interface clock for all active channels.

The configuration settings of the MC92604 affect the legal range of clock frequencies at which it may be operated. Table 5-1 shows legal transmit interface clock frequencies for all modes of operation. All transmit interface clock inputs, XMIT x CLK, and the PLL reference clock inputs, REF CLK, must have identical frequencies. The transmit data interface tolerates  $\pm 180^{\circ}$  of transmit interface clock phase drift relative to the PLL reference clock input.

#### 2.3.1 **Transmit Driver Operation**

The transmit driver outputs the transmission characters serially across the link. Two bits per internal transceiver clock, rx clock, one each on the rising and falling clock edges, are transmitted differentially from the XLINK x P/XLINK x N outputs. The internal rx clock runs at 625 MHz for 1-Gbps (1.25-Gbaud) operation and 312.5 MHz for 500-Mbps (625-Mbaud) operation.

The transmitter driver (high-speed serial link outputs) is a controlled impedance driver. The impedance of the driver is programmable to 50 or 75  $\Omega$  through the MEDIA configuration signal. The drive impedance is 50  $\Omega$  when MEDIA is low and 75  $\Omega$  when high.

#### 2.3.2 **Repeater Mode Operation**

Although repeater mode is primarily used for factory engineering, it may be used by the application as described in Section 5.5, "Repeater Mode." The repeater enable signal, REPE, should be configured low during a normal transceiver operation.

#### **Backplane Application Modes (COMPAT = Low)** 2.4

When the configuration control signal, COMPAT, is low, the MC92604 is in the 'backplane application mode.' In this application mode, the MC92604 transmitters accept either uncoded data, where the input data is encoded internally by an 8B/10B encoder, or coded data, where the input data is pre-encoded and the internal encoder is bypassed.

The interface for the backplane application mode is either 8 or 10 bits wide, or optionally 4 or 5 bits, as shown in Table 2-2.

MC92604 Dual Gigabit Ethernet Transceiver Reference Manual, Rev. 1

### 2.4.1 Transmitting Uncoded Data—8-/4-Bit Modes

The settings for the transmitter control signals when sending uncoded 8-bit or reduced interface 4-bit data is shown in Table 2-3.

When XMIT\_x\_ENABLE is low, an IDLE (K28.5) code group of proper running disparity is generated. The states of the XMIT\_x\_7-XMIT\_x\_0, XMIT\_x\_K, and XMIT\_x\_ERR signals are ignored. This allows the link partner's receiver to maintain alignment when transmission of data is not needed.

| XMIT_x_ENABLE | XMIT_x_ERR | XMIT_x_K   | Description                                                                                                                                                      |

|---------------|------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low           | Don't care | Don't care | Transmit <i>IDLE</i> (K28.5), ignore XMIT_x_7–XMIT_x_0 data inputs                                                                                               |

| High          | Low        | Low        | Transmit data present on XMIT_x_7-XMIT_x_0 data inputs                                                                                                           |

| High          | Low        | High       | Transmit control data present on XMIT_x_7–XMIT_x_0 data inputs                                                                                                   |

| High          | Low        | High       | Transmit disparity-style word synchronization event if XMIT_x_7-0 data inputs = 0xAD. The transmitter inputs will be ignored while sending these 16 code groups. |

| High          | High       | Don't care | Create an invalid 10-bit code group to be transmitted                                                                                                            |

Table 2-3. Transmitter Control States for Uncoded Data (TBIE = Low)

When XMIT\_x\_ENABLE is high, uncoded data is presented in 8-/4-bit bytes to the input register through the XMIT\_x\_7-XMIT\_x\_0 signals. The uncoded data is coded into 10-bit transmission code groups using an on-chip 8B/10B encoder. 8B/10B coding ensures DC balance across the link and sufficient transition density to facilitate reliable data and clock recovery. The XMIT\_x\_7-XMIT\_x\_0 signals are interpreted as normal data when the XMIT x K signal is low.

The 8B/10B code set includes 12 special control codes. Special control codes may be transmitted by setting the XMIT\_x\_K high as indicated in Table 2-3. There are only 12 valid control code groups; if the data input is other than the 12 defined values, then an illegal 10-bit code group will be generated and transmitted. Invalid combinations of XMIT\_x\_K and XMIT\_x\_7-XMIT\_x\_0 will generate invalid 10-bit code groups.

If XMIT x ERR is high then the 8B/10B encoder is forced to produce an invalid 10-bit code.

When using the device in a system where word alignment is required, it may be desirable to generate disparity-style word synchronization events. Also, it may be necessary to generate a disparity-style synchronization event for compatibility with legacy transceivers. A disparity-style word synchronization event is generated by setting the transmit data inputs to a 0xAD and asserting XMIT\_x\_K high for the appropriate transmitter(s). The transmitter generates 1 of 2 unique 16-code group IDLE (K28.5) sequences depending on the current running disparity:

where I+ stands for K28.5 of positive disparity, and I- stands for K28.5 of negative disparity.

2-6 Freescale Semiconductor

The transmitter inputs,  $XMIT_x_7-XMIT_x_0$ ,  $XMIT_x_K$ ,  $XMIT_x_ERR$ , and  $XMIT_x_ENABLE$  are ignored for the next 15 byte-times while this 16-code group sequence is transmitted.

Transmitting uncoded data in backplane applications with the reduced interface mode is shown in Table 2-4. The transmitter functional operation is the same as discussed above, except the data is entered on both edges of the transmitter input clock,  $XMIT_x_CLK$ .

Table 2-4. Transmitter Inputs for Reduced Uncoded Data—Backplane Mode

| Data on Rising Edge of XMIT_x_CLK | Data on Falling Edge of XMIT_x_CLK | MC92604 Signal Name |  |  |  |

|-----------------------------------|------------------------------------|---------------------|--|--|--|

| XMIT_x_ENABLE                     | XMIT_x_ENABLE (XOR) XMIT_x_ERR     | XMIT_x_ENABLE       |  |  |  |

| XMIT_x_K                          | Unused                             | XMIT_x_K            |  |  |  |

| Data bits 3-0                     | Data bits 7–4                      | XMIT_x_3/XMIT_x_0   |  |  |  |

The 8 bits of uncoded data are entered with the least significant nibble on the rising clock and the most significant nibble on the falling clock edge.

#### NOTE

When operating with the reduced data interface the MC92604 input pins, XMIT x 7–XMIT x 4, are unused and should be terminated low.

### 2.4.2 Transmitting Coded Data—10-/5-Bit Modes

This operating mode is specified when the TBIE input is high. The state of COMPAT input does not affect the transmitter's operation.

In this mode, 10-bit coded data may be transmitted, bypassing the internal 8B/10B encoder. The 10 bits of data to transmit are presented on the XMIT $_x$ 7–XMIT $_x$ 0 inputs along with bits 9 and 8 on the XMIT $_x$ ERR and XMIT $_x$ ENABLE inputs, respectively. The 10-bit coded data is transmitted as shown in Table 2-5.

Table 2-5. Transmitter Input States for Coded Data (TBIE = High)

| XMIT_x_K         | XMIT_x_ERR | XMIT_x_ENABLE | XMIT_ <i>x</i> _7–<br>XMIT_ <i>x</i> _0 | Description   |  |

|------------------|------------|---------------|-----------------------------------------|---------------|--|

| Used by receiver | Data bit 9 | Data bit 8    | Data bits 7–0                           | Data bits 9–0 |  |

The XMIT\_x\_K signal is ignored by the transmitter in the backplane 10-/5-bit modes, but, it is used by the receiver.

Freescale Semiconductor 2-7

#### **Transmitter**

When using the MC92604 in the backplane applications (COMPAT = low), it is not necessary to use the 8B/10B code set. However, special care must be taken. The data must exhibit the same properties as 8B/10B coded data. DC balance must be maintained and there must be sufficient transition density to ensure reliable clock and data recovery at the receiver. If running in the Ethernet TBI or RTBI mode, the data will be 8B/10B data.

#### NOTE

If the code used is not 8B/10B, then it must support the K28.5 IDLE code (this only applies to backplane mode; Ethernet-TBI mode is assumed to use 8B/10B). The code must be such to guarantee that no two codes, when concatenated, produce the 8-bit COMMA pattern as defined above.

The receivers require that COMMA code groups (K28.1, K28.5, or K28.7) be transmitted for byte synchronization. The 8-bit pattern ('00111110xx' or '11000001xx,' ordered from bits 0–7) is used for alignment and link-to-link synchronization when operating in any of the byte or word synchronization modes. The pattern of code groups and data required to achieve word synchronization (available only in backplane application mode, COMPAT = low) depends on the configuration of the receiver. The appropriate sequence must be applied through the 10-/5-bit interface.

Transmitting coded data with the reduced interface mode is shown in Table 2-6. The transmitter functional operation is the same as discussed above, except the data is entered on both edges of the transmitter input clock,  $XMIT_x_CLK$ .

Data on Rising Edge of XMIT\_x\_CLK

Data on Falling Edge of XMIT\_x\_CLK

MC92604 Signal Name

Data bit 4

Data bit 9

XMIT\_x\_ENABLE

Data bits 3-0

Data bits 8-5

XMIT\_x\_3/XMIT\_x\_0

Table 2-6. Transmitter Inputs for RTBI Operating Mode

The 10 bits of uncoded data are entered with the least significant 5 bits on the rising clock and the most significant bits on the falling clock edge.

2-8 Freescale Semiconductor

### 2.5 Ethernet Compliant Applications Modes (COMPAT = High)

The MC92604 Gigabit Ethernet transceiver was designed with the intent to meet the requirements of **IEEE Std 802.3-2002 [4]** for 1000BASE-X PHYs.

When the configuration control signal, COMPAT, is high, the MC92604 is in the 'Ethernet compliant application mode.' In this application mode, the MC92604 transmitters accept either uncoded data (GMII or RGMII interface), where the input data is encoded internally by an 8B/10B encoder, or coded data (TBI or RTBI interface), where the input data is pre-encoded and the internal encoder is bypassed. See Table 2-2 for these interface modes. Table 2-7 defines the ordered\_sets that are associated with the Gigabit Ethernet protocol.

| Code | Ordered_Set       | Number of Code-Groups | Encoding                         |  |  |  |  |  |  |

|------|-------------------|-----------------------|----------------------------------|--|--|--|--|--|--|

| /C/  | Configuration     | _                     | Alternating /C1/ and /C2/        |  |  |  |  |  |  |

| /C1/ | Configuration 1   | 4                     | /K28.5/D21.5/Config_Reg          |  |  |  |  |  |  |

| /C2/ | Configuration 2   | 4                     | /K28.5/D2.2/Config_Reg           |  |  |  |  |  |  |

|      |                   |                       |                                  |  |  |  |  |  |  |

| /I/  | IDLE              | _                     | Correcting /I1/, Preserving /I2/ |  |  |  |  |  |  |

| /11/ | IDLE1             | 2                     | /K28.5/D5.6/                     |  |  |  |  |  |  |

| /12/ | IDLE2             | 2                     | /K28.5/D16.2/                    |  |  |  |  |  |  |

|      | Encapsulation     |                       |                                  |  |  |  |  |  |  |

| /R/  | Carrier_Extend    | 1                     | /K23.7/                          |  |  |  |  |  |  |

| /S/  | Start_of_Packet   | 1                     | /K27.7/                          |  |  |  |  |  |  |

| /T/  | End_of_Packet     | 1                     | /K29.7/                          |  |  |  |  |  |  |

| /V/  | Error_Propagation | 1                     | /K30.7/                          |  |  |  |  |  |  |

**Table 2-7. Gigabit Ethernet Defined Ordered Sets**

### 2.5.1 Transmitting Uncoded Data—GMII or RGMII Modes

The following sections discuss the operating process for uncoded data (GMII or RGMII interface) transmissions.

### 2.5.1.1 Auto-Negotiation Process

Operating in the Ethernet compatibility mode, the MC92604 implements the auto-negotiation function at the PCS sublayer for 1000BASE-X as defined in Clause 37 of IEEE Std 802.3-2002 specification [4].

The transmitter enters auto-negotiate mode (if auto-negotiate is enabled) when one of five events occur.

- The part is reset

- The part is requested to restart the auto-negotiation process through the MDIO interface

- The part is reconfigured through the MDIO interface

- The associated receiver loses byte synchronization

- The associated receiver detects an auto-negotiate sequence initiated by its link partner

MC92604 Dual Gigabit Ethernet Transceiver Reference Manual, Rev. 1

Freescale Semiconductor 2-9

#### **Transmitter**

When an auto-negotiate sequence is started, the transmitter initially sends at least 10 milliseconds of /C1/C2/ sequences with all zeros as the Configuration Register contents. This forces the remote device to also enter auto-negotiate mode.

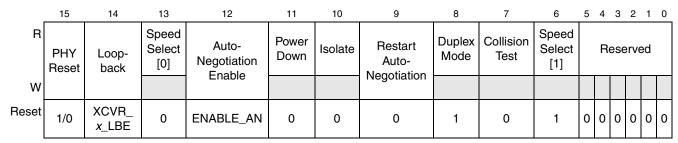

The contents of the configuration register are continuously sent until the associated receiver detects the compatible configuration being sent from the link partner. The MC92604 is configured as full-duplex 1-Gigabit; therefore, the configuration is as shown in Figure 2-2. For register details, see Section 4.2.4, "MDIO RA 4—Auto-Negotiation Advertisement Register."

| Bit      | 15                        | 14               | 13               | 12               | 11       | 10 | 9                | 8                | 7               | 6               | 5        | 4 | 3 | 2 | 1 | 0 |

|----------|---------------------------|------------------|------------------|------------------|----------|----|------------------|------------------|-----------------|-----------------|----------|---|---|---|---|---|

| Function | Next<br>Page <sup>1</sup> | Ack <sup>2</sup> | RF2 <sup>3</sup> | RF1 <sup>3</sup> | Reserved |    | PS2 <sup>4</sup> | PS1 <sup>4</sup> | HD <sup>5</sup> | FD <sup>6</sup> | Reserved |   |   |   |   |   |

| Value    | 0                         | 1/0              | 1/0              | 1/0              | 0        | 0  | 0                | 0                | 0               | 0               | 1        | 0 | 0 | 0 | 0 | 0 |

<sup>&</sup>lt;sup>1</sup> Next Page—MC92604 does not support multiple pages of configuration registers.

#### Figure 2-2. Configuration Register

The 'Ack' bit is asserted when three consecutive matching configuration register values are received. The auto-negotiate state is complete when three consecutive matching configuration register values are received with the 'Ack' bit set. The transmitter continues sending auto-negotiate sequences once the auto-negotiate sequence is complete for at least 10 ms.

#### NOTE

See the state diagram in Figure 37-6 of the IEEE Std. 802.3-2002 specification [4] for a complete description.

#### 2.5.1.2 Ethernet Data Transmission Process

Transmitter operation is controlled by the two input control signals XMIT\_x\_ENABLE and XMIT x ERR. See Table 3-8 for the complete GMII interface to the MC92604.

When both XMIT\_x\_ENABLE and XMIT\_x\_ERR inputs are low, the transmitter broadcasts IDLE Ordered\_sets. Whenever a new series of IDLE Ordered\_sets are started, the first IDLE Ordered\_set may be an I1 Ordered\_set to correct the running disparity, all subsequent IDLE Ordered sets will be I2s. The transmitter must be aware of even/oddness. K28.5 code groups are transmitted as the 'even' code group and either D5.6 or D16.2 as the 'odd' code group. This even/odd flag is set at initialization and must be maintained since other events will depend on this even/oddness.

When XMIT\_x\_ENABLE is raised, the data on the XMIT\_x\_7 through XMIT\_x\_0 inputs is assumed to be the first byte of an 8-byte preamble. The preamble usually consists of 7 consecutive 0x55 code groups followed by a 0xD5 code group. The transmitter replaces the first 0x55 code group in the preamble with a

2-10 Freescale Semiconductor

<sup>&</sup>lt;sup>2</sup> Ack—Asserted when the receiver detects a valid configuration from the other transmitter.

<sup>&</sup>lt;sup>3</sup> RF1 and RF2— 'Remote faults' as detected by the receiver.

<sup>&</sup>lt;sup>4</sup> PS1 and PS2—Pause control bits that reflect the values of MDIO register 4's bits 12 and 13, respectively. This register may be modified via the MDIO interface.

<sup>&</sup>lt;sup>5</sup> HD—MC92604 does not support half-duplex mode.

<sup>&</sup>lt;sup>6</sup> FD—MC92604 always runs in full-duplex mode.

/S/ Ordered\_set to indicate Start\_of\_Frame. The MC92604 will support shorter preambles. The minimum preamble size is a single 0x55 code group followed by a 0xD5 code group.

If XMIT\_x\_ERR is also raised when XMIT\_x\_ENABLE is raised, then a false carrier is declared, and a void code groups (/V/) is transmitted.

If XMIT\_x\_ERR is raised after XMIT\_x\_ENABLE has been raised and while data is being transferred, this is a request to transmit an error propagation Ordered\_set (/V/) for as many code groups as long as XMIT x ERR remains high.

When a normal End\_of\_Packet is detected (XMIT\_x\_ENABLE transitions to low and XMIT\_x\_ERR remains low), a single End\_of\_Packet ordered\_set (/T/) is transmitted followed by at least one Carrier\_Extend (/R/) ordered\_set. A second Carrier\_Extend will be inserted (if necessary) to complete an even/odd pair. This is then followed by IDLE ordered\_sets to indicate the inter-packet gap. The first /I/ may be either an /I1/ or /I2/, depending on running disparity.

If XMIT\_x\_ERR transitions to high as XMIT\_x\_ENABLE transitions to low, this is defined as a 'carrier extension.' The 'carrier extension' state is a half-duplex feature and is not supported in the MC92604.

XMIT x ERR will be ignored while XMIT x ENABLE is low.

Transmitting in the Ethernet-compatability mode with the reduced (RGMII) interface is shown in Table 2-8. The transmitter functional operation is the same as discussed above, except the data is entered on both edges of the transmitter input clock, XMIT x CLK.

Data on Rising Edge of XMIT\_x\_CLK

Data on Falling Edge of XMIT\_x\_CLK

MC92604 Signal Name

GMII\_TX\_EN

GMII\_TX\_EN (XOR) GMII\_TX\_ER

XMIT\_x\_ENABLE

Data bits 3-0

Data bits 7-4

XMIT\_x\_3/XMIT\_x\_0

Table 2-8. Transmitter Inputs for RGMII Operating Mode

The 8 bits of uncoded data are entered with the least significant 4 bits on the rising clock and the most significant bits on the falling clock edge.

### 2.5.2 Transmitting Coded Data—TBI or RTBI Modes

The PMA sublayer of the 1000BASE-X specification does not require any functional differences in the transmitter from that used in the backplane application mode. Therefore, when operating in a mode specified when the TBIE input is high, the state of the COMPAT input does not affect the transmitter's operation. See Section 2.4.2, "Transmitting Coded Data—10-/5-Bit Modes."

Freescale Semiconductor 2-11

**Transmitter**

### 2.6 Transmitter Redundant Link Operation

The MC92604 is configured as a single channel SerDes, with redundant link input and outputs, if the enable redundancy signal, ENAB\_RED, is asserted high. Only the data interface to channels A will accept data to be transmitted. This data will be transmitted over the appropriate link as specified by the BROADCAST and XCVR\_RSEL inputs as shown in Table 2-9.

#### NOTE

When operating in the redundancy mode, the B input signals (XMIT\_B\_---), should be terminated low.

XCVR\_RSEL selects the primary or secondary link I/Os. The BROADCAST control signal enables both channel A and B link outputs to transmit data at their data interface, while enabling the receiver links to receive serial data defined by the XCVR\_RSEL control signal. See Section 3.3.6, "Receiver Redundant Link Operation," for more on receiver redundancy.

ENAB\_RED **BROADCAST** XCVR\_RSEL **Action** Data transmitted over XLINK\_A\_P/XLINK\_A\_N Do Not Care Do Not Care 1 0 0 Data transmitted over XLINK\_A\_P/XLINK\_A\_N Data transmitted over XLINK\_B\_P/XLINK\_B\_N 1 0 1 Do Not Care Data transmitted over XLINK\_A\_P/XLINK\_A\_N and XLINK\_B\_P / 1 XLINK\_B\_N

**Table 2-9. Transmit Redundant Link Operation**

2-12 Freescale Semiconductor

# **Chapter 3 Receiver**

This chapter describes the MC92604 receiver, its interfaces, and operation. This chapter consists of the following sections:

- Section 3.1, "Receiver Block Diagram"

- Section 3.2, "Receiver Interface Signals"

- Section 3.3, "Functional Description"

- Section 3.4, "Receiver Interface Configuration"

- Section 3.5, "Data Alignment Configurations"

- Section 3.6, "Receiver Interface Timing Modes"

- Section 3.7, "Ethernet Compliant Applications Modes (COMPAT = High)"

- Section 3.8, "Backplane Applications Modes (COMPAT = Low)"

Freescale Semiconductor 3-1

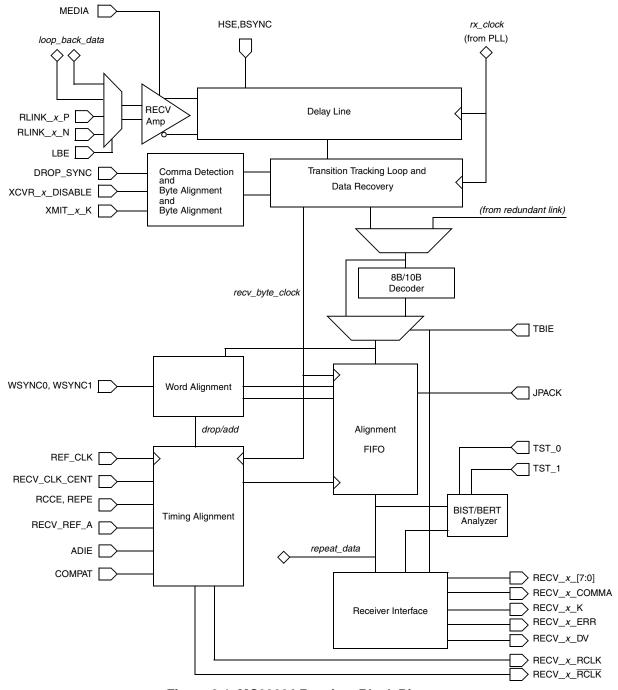

### 3.1 Receiver Block Diagram

Figure 3-1 shows the MC92604 receiver's block diagram.

Figure 3-1. MC92604 Receiver Block Diagram

3-2 Freescale Semiconductor

# 3.2 Receiver Interface Signals

This section describes the interface signals of the MC92604 receiver. Each signal's name, function, direction, and active state is described in Table 3-1. The table's signal names use the letter 'x' as a place holder for the link identifier letter 'A' and 'B.' Internal signals listed in the table are not available at the external interface of the device, but are presented to help illustrate the device's operation.

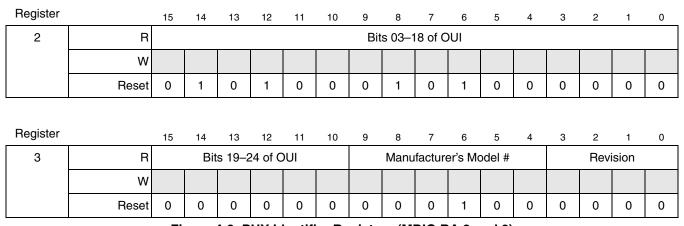

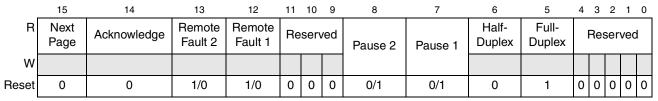

Table 3-1. MC92604 Receiver Interface Signals