# **CONNECTIVITY SOLUTIONS**

# **PI7C9X2G308GP**

# PCIe2 3-Port/8-Lane Packet Switch, GreenPacket™ Family

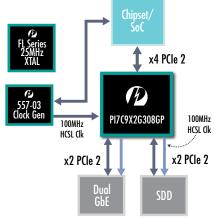

The PI7C9X2G308GP is an 8-lane PCI Express Gen 2 Switch with 3 PCI Express ports specifically designed to meet high performance and the latest GREEN low-power, lead (Pb)-free system requirements, such as Embedded, Storage, Network and other platforms. The name of the family, GreenPacket<sup>TM</sup>, refers to Pericom proprietary power saving technology.

The PI7C9X2G308GP provides one upstream port supporting x4, and two downstream ports that support x2 operation. The flexible upstream port provides users the flexibility to expand or fan-out from a wide range of x86, ARM, MIPS, PowerPC SoC/ Chipset, and it is a suitable solution for Embedded, Storage, HBA, Combo card, Surveillance, wired/ wireless Networking, and other applications.

## **Industry Specifications Compliance**

- → PCI Express® Base Specification, Revision 2.1

- → PCI Express CEM Specification, Revision 2.0

- → PCI-to-PCI Bridge Architecture Spec., Rev 1.2

- → Advanced Configuration Power Interface (ACPI)

- → Specification

- → SMBus interface support

#### **Applications**

- → NAS/ Storage

- → Server

- → HBA / Combo cards

- → Embedded system

- → IPC/ Industrial control

- → Automotive

- → Wireless AP/ Switch Router

- → Wired/ Wireless Tele/ data communication

- → Printer/ MFP/ Peripheral

- → Surveillance/ Security

- → Set-top box and consumer devices

- → NB/ PC Motherboard PCle slot expansion

#### **Ordering Information**

| Part Number         | Package  | PB-Free<br>& Green                      | Temperature   |

|---------------------|----------|-----------------------------------------|---------------|

| PI7C9X2G308GPANJEX† | 196 LBGA | YES                                     | -40°C TO 85°C |

| PI7C9X2G308GPAEVB   | Board    | Board Evaluation kit for PI7C9X2G308GPA |               |

#### † Note: Adding an X suffix =Tape/Reel

### **Features**

- → PCISIG PCI Express 2.1 certificated

- → Integrated 100MHz Clock buffer for each downstream port

- → Reliability, Availability and Serviceability

- o Supports Data Poisoning and End-to-End CRC

- Advanced Error Reporting and Logging

- → Device State Power Management

- o Supports D0, D3Hot and D3Cold device power states

- → Advanced Power Savings

- o Empty downstream ports are set to idle

- Programmable driver current and de-emphasis level at each individual port

- → Port Arbitration: Round Robin (RR), Weighted RR and Time-based Weighted RR

- → Extended Virtual Channel capability

- o Two Virtual Channels (VC) and Eight Traffic Class (TC) support

- o Independent TC/VC mapping for each port

- → Supports Isochronous Traffic

- Isochronous traffic class mapped to VC1 only

- → Supports "Cut-through" (Default) as well as "Store and Forward" mode for switching packets

- → Peer-to-peer switching between any two downstream ports

- → Supports up to 512-byte maximum payload size

- → Power Dissipation: 1.3 W typical in LO normal mode (Including clock buffer Pd)

- → Industrial Temperature Range: -40°C to 85°C

- → MTBF: 50, 927, 360 hours

- → Package: 196-pin LBGA 15mm x 15mm o Pb free and 100% Green

## **Enhanced Features**

- → 150ns typical latency for packet running through switch without blocking

- → Link Power Management

- o Supports LO, LOs, L1, L2, L2/L3Ready and L3 link power states

- o Active state power management for LOs and L1 states

- o Supports PCI-PM and ASPM of L1.1 PM Sub-state

- → Supports Device Specific PME Turn-Off Message for each downstream port

- → Supports Access Control Service (ACS) for peer-to-peer traffic

- → Supports Address Translation (AT) packet for SR-IOV application

- → Supports OBFF and LTR

- → Supports Serial Hot Plug Controller